ASIC per LLM e chip specializzati per l'inferenza (e perché sono importanti)

Gli ASIC e i silicio personalizzati migliorano velocità ed efficienza dell'inferenza degli LLM.

Il futuro dell’AI non riguarda solo modelli più intelligenti. Riguarda anche il silicio che corrisponde al modo in cui questi modelli vengono effettivamente eseguiti. L’hardware specializzato per l’inference degli LLM sta seguendo una strada che ricorda il passaggio del mining di Bitcoin dalle GPU agli ASIC costruiti appositamente, sebbene con vincoli più stringenti perché modelli e schemi di precisione continuano a evolversi.

Per ulteriori informazioni su throughput, latenza, VRAM e benchmark su runtime e hardware, consulta LLM Performance: Benchmark, Colli di Bottiglia e Ottimizzazione.

Immaginazione Elettrica - Flux text to image LLM.

Immaginazione Elettrica - Flux text to image LLM.

Perché gli LLM beneficiano di hardware specifico per l’inference

I Large language models hanno trasformato l’[AI](https://www.glukhov.org/it/ai-devtools/ai-coding-assistants/ “Confronto degli assistenti di coding AI}), ma ogni risposta fluente dipende da enormi e prevedibili flussi di matematica matriciale e traffico di memoria. Poiché la spesa per l’inference cresce — spesso superando quella per l’addestramento durante il ciclo di vita di un modello — i chip ottimizzati per il serving, e non per ogni possibile carico di lavoro, diventano economicamente attraenti.

L’analogia con il mining di Bitcoin è imperfetta ma istruttiva. Entrambi sono compiti ripetitivi e ben delimitati, dove eliminare la generalità non utilizzata dal die può acquistare grandi guadagni in throughput e joule per operazione utile.

Cosa suggerisce la storia del mining di Bitcoin sugli ASIC per l’inference

Il mining di Bitcoin è evoluto attraverso quattro generazioni:

| Era | Hardware | Vantaggio Chiave | Limitazione |

|---|---|---|---|

| 2015–2020 | GPU (CUDA, ROCm) | Flessibilità | Consumi energetici elevati, limitazioni di memoria |

| 2021–2023 | TPUs, NPUs | Specializzazione a grana grossa | Ancora orientato all’addestramento |

| 2024–2025 | Transformer ASICs | Ottimizzati per inference a bassa bit | Generalità limitata |

L’AI sta seguendo un percorso simile. Ogni transizione ha migliorato le prestazioni e l’efficienza energetica di ordini di grandezza.

Tuttavia, a differenza degli ASIC per Bitcoin (che calcolano solo SHA-256), gli ASIC per l’inference necessitano di una certa flessibilità. I modelli evolvono, le architetture cambiano e gli schemi di precisione migliorano. Il trucco è specializzarsi giustamente — cablando i pattern principali mantenendo l’adattabilità ai bordi.

Come l’inference degli LLM differisce dall’addestramento (e cosa sfruttano i chip)

I carichi di lavoro di inference espongono pattern che l’hardware specializzato può colpire:

- La bassa precisione domina — 8-bit, 4-bit, persino aritmetica ternaria o binaria funzionano bene per l’inference

- La memoria è il collo di bottiglia — Spostare pesi e cache KV consuma molta più energia rispetto al calcolo

- La latenza conta più del throughput — Gli utenti si aspettano token in meno di 200ms

- Parallelismo massiccio delle richieste — Migliaia di richieste di inference concorrenti per chip

- Pattern prevedibili — I livelli Transformer sono altamente strutturati e possono essere cablati

- Opportunità di sparsità — I modelli utilizzano sempre più tecniche di potatura e MoE (Mixture-of-Experts)

Un chip per l’inference costruito su misura può cablare queste assunzioni per ottenere 10–50× migliori prestazioni per watt rispetto alle GPU a scopo generale.

Chi sta costruendo silicio ottimizzato per l’inference LLM

Il mercato degli ASIC per l’inference spazia dai leader consolidati, ai design su scala di wafer, fino alle startup che scommettono su silicio a forma di transformer:

| Azienda | Chip / Piattaforma | Specialità |

|---|---|---|

| Groq | LPU (Language Processing Unit) | Throughput deterministico per LLM |

| Etched AI | Sohu ASIC | Motore Transformer cablato |

| Tenstorrent | Grayskull / Blackhole | ML generale con mesh a banda larga |

| Taalas | HC1 (prodotto Llama 3.1 8B) / roadmap HC2 | Silicio “hardcore” specifico per modello; fonde storage e calcolo |

| OpenAI × Broadcom | Chip Inference Personalizzato | Lancio previsto per il 2026 |

| Intel | Crescent Island | GPU Xe3P solo per inference con 160GB HBM |

| Cerebras | Wafer-Scale Engine (WSE-3) | Enorme bandwidth di memoria on-die |

Molto di questo è già nei data center in produzione, non solo nella presentazione. Team più piccoli come d-Matrix, Rain AI, Mythic e Tenet stanno perseguendo architetture ottimizzate per l’inference a bassa bit e sparsità strutturata.

Taalas HC1, Chat Jimmy e serving ultra-veloce di piccoli modelli

Taalas è un esempio recente della scuola “specializzare quasi tutto”. L’azienda sostiene che il confine memoria-calcolo (DRAM fuori chip rispetto a SRAM on-chip) domini costi, potenza e complessità ingegneristica per l’inference, e che il silicio per modello — quello che chiamano Hardcore Models — può collassare quel confine quando un deployment è disposto a fissare i pesi e il grafo.

Il loro primo prodotto in spedizione, HC1, cabla una variante di Llama 3.1 8B. Questa scelta è pragmatica: il modello è abbastanza piccolo da essere lanciato rapidamente, documentato apertamente e ancora utile per molti compiti di automazione, classificazione e stesura dove la profondità del ragionamento puro conta meno rispetto a latenza e costo. Taalas riferisce un ordine di grandezza di 16k–17k token decodificati al secondo per utente per questa configurazione (metodologia del fornitore e confronti appaiono nel loro report), insieme a affermazioni di grandi guadagni in capitale e potenza rispetto agli stack GPU convenzionali per la stessa classe di modello. I componenti di prima generazione utilizzano un archiviazione mista a bassa bit aggressiva; l’azienda descrive il passaggio verso formati floating-point a 4 bit standard su HC2 per recuperare margine sulla qualità.

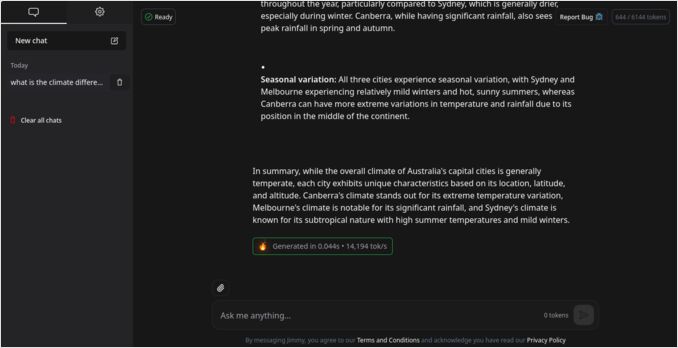

Per gli sviluppatori che vogliono capire cosa implichi quella classe di throughput in pratica, Taalas esegue un demo di chatbot gratuito, Chat Jimmy, e offre accesso API tramite un modulo di applicazione sul loro sito. È esplicitamente un proof of concept — non un assistente di frontiera — ma illustra un pubblico reale che potrebbe preferire un modello modesto a “velocità della cognizione umana” rispetto a un modello più grande che sembra lento o costoso.

Architettura di un ASIC per l’inference Transformer

Com’è realmente un chip ottimizzato per i transformer sotto il cofano?

+--------------------------------------+

| Interfaccia Host |

| (PCIe / CXL / NVLink / Ethernet) |

+--------------------------------------+

| Interconnessione On-chip (mesh/anello) |

+--------------------------------------+

| Mattoni di Calcolo / Core |

| — Unità di moltiplicazione matriciale densa |

| — ALU a bassa precisione (int8/int4) |

| — Unità di Dequant / Attivazione |

+--------------------------------------+

| SRAM On-chip & buffer cache KV |

| — Pesi caldi, cache fuse |

+--------------------------------------+

| Pipeline di Quantizzazione / Dequant |

+--------------------------------------+

| Scheduler / Controller |

| — Motore di esecuzione del grafo statico |

+--------------------------------------+

| Interfaccia DRAM / HBM Off-chip |

+--------------------------------------+

Le caratteristiche architetturali chiave includono:

- Core di calcolo — Unità di moltiplicazione matriciale densa ottimizzate per operazioni int8, int4 e ternarie

- SRAM On-chip — Buffer grandi ospitano pesi caldi e cache KV, minimizzando costosi accessi alla DRAM

- Interconnessioni streaming — Topologia mesh abilita un scaling efficiente su più chip

- Motori di quantizzazione — Quantizzazione/dequantizzazione in tempo reale tra i livelli

- Stack del compilatore — Traduce grafi PyTorch/ONNX direttamente in micro-operazioni specifiche del chip

- Kernel di attenzione cablati — Elimina l’overhead del flusso di controllo per softmax e altre operazioni

La filosofia di progettazione rispecchia gli ASIC di Bitcoin: ogni transistor serve il carico di lavoro specifico. Nessun silicio sprecato per funzionalità che l’inference non ha bisogno.

Benchmark GPU contro ASIC per l’inference LLM

Le figure pubbliche rappresentative mostrano come l’hardware specializzato per l’inference possa distaccarsi dagli stack GPU a scopo generale sulle stesse famiglie di modelli (verifica sempre la metodologia e le assunzioni di batch per i tuoi carichi di lavoro):

| Modello | Hardware | Throughput (token/s) | Tempo al Primo Token | Moltiplicatore Prestazioni |

|---|---|---|---|---|

| Llama-2-70B | NVIDIA H100 (8x DGX) | ~80–100 | ~1.7s | Linea base (1×) |

| Llama-2-70B | Groq LPU | 241–300 | 0.22s | 3–18× più veloce |

| Llama-3.3-70B | Groq LPU | ~276 | ~0.2s | Costante 3× |

| Gemma-7B | Groq LPU | 814 | <0.1s | 5–15× più veloce |

| Llama-3.1-8B | Taalas HC1 (fornitore) | ~16k–17k decode t/s/utente | — | Asse separato (grafo 8B fisso, non 70B) |

Fonti: Groq.com, ArtificialAnalysis.ai, Blog Sviluppatore NVIDIA; figure Taalas HC1 dal post prodotto dell’azienda.

Le righe focalizzate su Groq mostrano grandi guadagni in throughput e tempo al primo token rispetto a una linea base GPU high-end su modelli grandi. La riga Taalas non è un altro moltiplicatore rispetto a quelle linee da 70B; illustra quanto lontano si possa spingere la decodifica per utente quando il modello e il grafo sono fissi nel silicio, a costo di flessibilità.

Compromessi quando si specializza il silicio per l’inference

La specializzazione acquista prestazioni, ma reintroduce rischi di prodotto e ingegneria:

-

Flessibilità vs. Efficienza. Un ASIC completamente fisso attraversa i modelli transformer di oggi, ma potrebbe avere difficoltà con le architetture di domani. Cosa succede quando i meccanismi di attenzione evolvono o emergono nuove famiglie di modelli?

-

Quantizzazione e Accuratezza. La precisione più bassa salva enormi quantità di energia, ma gestire il degrado dell’accuratezza richiede schemi di quantizzazione sofisticati. Non tutti i modelli quantizzano bene a 4 bit o meno.

-

Ecosistema Software. L’hardware senza compilatori robusti, kernel e framework è inutile. NVIDIA domina ancora largamente a causa dell’ecosistema maturo di CUDA. I nuovi produttori di chip devono investire pesantemente nel software.

-

Costo e Rischio. Tape-out di un chip costa decine di milioni di dollari e richiede 12–24 mesi. Per le startup, questa è una scommessa massiccia su assunzioni architetturali che potrebbero non reggere.

Tuttavia, su scala iper-scala, anche guadagni di efficienza del 2× si traducono in miliardi di risparmi. Per i cloud provider che eseguono milioni di richieste di inference al secondo, il silicio personalizzato è sempre più non negoziabile.

Una lista dei desideri per un chip LLM per l’inference

| Funzione | Specifica Ideale |

|---|---|

| Processo | Nodo 3–5nm |

| SRAM On-chip | 100MB+ strettamente accoppiato |

| Precisione | Supporto nativo int8 / int4 / ternario |

| Throughput | 500+ token/sec (modello 70B) |

| Latenza | <100ms tempo al primo token |

| Interconnessione | Mesh a bassa latenza o link ottici |

| Compilatore | PyTorch/ONNX → toolchain microcodice |

| Energia | <0.3 joule per token |

Sguardi al futuro (2026–2030)

Aspettatevi che il panorama dell’hardware per l’inference si stratifichi in tre livelli grezzi:

-

Chip per l’addestramento. GPU high-end come NVIDIA B200 e AMD Instinct MI400 continueranno a dominare l’addestramento con la loro flessibilità FP16/FP8 e enorme bandwidth di memoria.

-

ASIC per l’inference. Acceleratori Transformer cablati, a bassa precisione, gestiranno il serving in produzione su scala iper-scala, ottimizzati per costo ed efficienza.

-

NPU Edge. Chip piccoli e ultra-efficienti porteranno LLM quantizzati a smartphone, veicoli, dispositivi IoT e robot, abilitando l’intelligenza on-device senza dipendenza dal cloud.

Oltre all’hardware da solo, vedremo:

- Cluster ibridi — GPU per addestramento flessibile, ASIC (o motori di inference su scala di wafer) per serving efficiente

- Inference-as-a-Service — Iper-scaler che mescolano acceleratori di prima parte (AWS Inferentia, Google TPU, ecc.) con GPU

- Co-design hardware–software — Modelli plasmati per sparsità a blocchi, instradamento MoE e livelli amichevoli alla quantizzazione

- Silicio per modello o per famiglia — Società come Taalas che scommettono che alcuni deployment scambieranno la flessibilità architetturale per costi e latenza estremi su un grafo noto

- API di inference open — Pressione per mantenere le interfacce di serving portabili anche quando il silicio non lo è

Pensieri finali

La “ASIC-izzazione” dell’inference AI è già in corso. Proprio come il mining di Bitcoin è evoluto dalle CPU a silicio specializzato, il deployment AI sta seguendo la stessa strada.

La prossima rivoluzione dell’AI non riguarderà modelli più grandi — riguarderà chip migliori. L’hardware ottimizzato per i pattern specifici dell’inference transformer determinerà chi potrà deployare l’AI economicamente su scala.

Proprio come i minatori di Bitcoin hanno ottimizzato via ogni watt sprecato, l’hardware per l’inference estrarrà ogni ultimo FLOP-per-joule. Quando accadrà, la vera svolta non sarà negli algoritmi — sarà nel silicio che li esegue.

Il futuro dell’AI sta venendo inciso nel silicio, un transistor alla volta.

Per ulteriori benchmark, scelte hardware e tuning delle prestazioni, controlla il nostro hub LLM Performance: Benchmark, Colli di Bottiglia e Ottimizzazione.

Link Utili

- Benchmark Ufficiali Groq

- Taalas — Il percorso verso un’AI ubiquitaria (HC1, roadmap, filosofia)

- Chat Jimmy — Demo Taalas Llama 3.1 8B

- Modulo richiesta accesso API Taalas

- Artificial Analysis - Leaderboard Prestazioni LLM

- Breve Tecnico NVIDIA H100

- Annuncio ASIC Transformer Etched AI

- Motore Wafer-Scale Cerebras

- Prezzi di NVidia RTX 5080 e RTX 5090 in Australia - Ottobre 2025

- LLM Performance e Lane PCIe: Considerazioni Chiave

- Test di velocità dei Large Language Models

- Confronto dell’idoneità delle GPU NVidia per l’AI

- La Quadro RTX 5880 Ada 48GB è buona?