ASIC pour LLM et puces d'inférence spécialisées (leur importance)

Les ASIC et les puces sur mesure augmentent la vitesse et l'efficacité de l'inférence des LLM.

L’avenir de l’IA ne concerne pas seulement des modèles plus intelligents. Il s’agit également de silicium adapté à la manière dont ces modèles sont réellement déployés. Le matériel spécialisé pour l’inférence des LLM emprunte une voie rappelant le passage du minage de Bitcoin des GPU aux ASIC conçus pour un usage spécifique, mais avec des contraintes plus strictes, car les modèles et les recettes de précision continuent d’évoluer.

Pour en savoir plus sur le débit, la latence, la VRAM et les benchmarks à travers les temps d’exécution et les matériels, consultez Performance des LLM : Benchmarks, Goulottes et Optimisation.

Imagination Électrique - Flux texte vers image LLM.

Imagination Électrique - Flux texte vers image LLM.

Pourquoi les LLM bénéficient d’un matériel spécifique à l’inférence

Les modèles de langage de grande taille ont transformé l’IA, mais chaque réponse fluide dépend de flux massifs et prévisibles de calculs matriciels et de trafic mémoire. À mesure que les dépenses d’inférence augmentent — dépassant souvent le coût de l’entraînement sur la durée de vie d’un modèle —, les puces optimisées pour le service (serving), et non pour chaque charge de travail possible, deviennent économiquement attractives.

L’analogie avec le minage de Bitcoin est imparfaite mais instructive. Il s’agit dans les deux cas de tâches répétitives et bien délimitées où l’élimination de la généralité inutilisée sur la puce peut procurer de grands gains en débit et en joules par opération utile.

Ce que l’histoire du minage de Bitcoin suggère pour les ASIC d’inférence

Le minage de Bitcoin a évolué à travers quatre générations :

| Ère | Matériel | Avantage clé | Limitation |

|---|---|---|---|

| 2015–2020 | GPU (CUDA, ROCm) | Flexibilité | Consommateur d’énergie, limité par la mémoire |

| 2021–2023 | TPU, NPU | Spécialisation à grain grossier | Toujours orienté entraînement |

| 2024–2025 | ASIC Transformer | Optimisé pour l’inférence à faible précision | Généralité limitée |

Le domaine de l’IA suit une voie similaire. Chaque transition a amélioré la performance et l’efficacité énergétique de plusieurs ordres de grandeur.

Cependant, contrairement aux ASIC de Bitcoin (qui ne calculent que SHA-256), les ASIC d’inférence ont besoin d’une certaine flexibilité. Les modèles évoluent, les architectures changent et les schémas de précision s’améliorent. L’astuce consiste à se spécialiser juste assez — coder les motifs principaux en dur tout en maintenant une adaptabilité sur les bords.

Comment l’inférence des LLM diffère de l’entraînement (et ce que les puces exploitent)

Les charges de travail d’inférence exposent des motifs que le matériel spécialisé peut cibler :

- La faible précision domine — L’arithmétique à 8 bits, 4 bits, voire ternaire ou binaire fonctionne bien pour l’inférence

- La mémoire est le goulot d’étranglement — Le déplacement des poids et des caches KV consomme beaucoup plus d’énergie que le calcul

- La latence importe plus que le débit — Les utilisateurs s’attendent à des tokens en moins de 200 ms

- Parallélisme massif des requêtes — Des milliers de requêtes d’inférence concurrentes par puce

- Motifs prévisibles — Les couches Transformer sont hautement structurées et peuvent être câblées en dur

- Opportunités de sparsité — Les modèles utilisent de plus en plus des techniques d’élagage et MoE (Mixture-of-Experts)

Une puce d’inférence conçue sur mesure peut câbler ces hypothèses en dur pour atteindre 10 à 50 fois de meilleures performances par watt que les GPU à usage général.

Qui construit du silicium d’inférence optimisé pour les LLM

Le marché des ASIC d’inférence s’étend des acteurs établis aux conceptions à l’échelle de la wafer et aux startups pariant sur un silicium en forme de Transformer :

| Entreprise | Puce / Plateforme | Spécialité |

|---|---|---|

| Groq | LPU (Language Processing Unit) | Débit déterministe pour les LLM |

| Etched AI | ASIC Sohu | Moteur Transformer câblé en dur |

| Tenstorrent | Grayskull / Blackhole | ML général avec maillage à large bande |

| Taalas | HC1 (produit Llama 3.1 8B) / HC2 roadmap | Silicium “cœur dur” spécifique au modèle ; fusionne stockage et calcul |

| OpenAI × Broadcom | Puce d’inférence personnalisée | Lancement annoncé pour 2026 |

| Intel | Crescent Island | GPU Xe3P dédié à l’inférence avec 160 Go HBM |

| Cerebras | Wafer-Scale Engine (WSE-3) | Bande passante mémoire massive sur puce memory bandwidth |

Une grande partie de cela est déjà dans les centres de données de production, pas seulement dans les diapositives. Des équipes plus petites comme d-Matrix, Rain AI, Mythic et Tenet poursuivent également des architectures adaptées à l’inférence à faible précision et à la sparsité structurée.

Taalas HC1, Chat Jimmy et le service ultra-rapide de petits modèles

Taalas est un exemple récent de l’école “spécialiser presque tout”. L’entreprise soutient que la frontière mémoire–calcul (DRAM hors puce contre SRAM sur puce) domine les coûts, la consommation d’énergie et la complexité d’ingénierie pour l’inférence, et que le silicium par modèle — ce qu’ils appellent des Modèles Hardcore — peut effacer cette frontière lorsqu’un déploiement accepte de figer les poids et le graphe.

Leur premier produit commercialisé, HC1, câble en dur une variante de Llama 3.1 8B. Ce choix est pragmatique : le modèle est suffisamment petit pour être déployé rapidement, documenté ouvertement et reste utile pour de nombreuses tâches d’automatisation, de classification et de rédaction où la profondeur du raisonnement brut compte moins que la latence et le coût. Taalas rapporte un ordre de grandeur de 16k–17k tokens décodés par seconde par utilisateur pour cette configuration (la méthodologie du fournisseur et les comparaisons figurent dans leur article), ainsi que des gains importants en capital et en énergie par rapport aux piles GPU conventionnelles pour la même classe de modèle. Les pièces de première génération utilisent un stockage mixte à faible précision agressif ; l’entreprise décrit une transition vers des formats flottants standard à 4 bits sur HC2 pour récupérer de la marge sur la qualité.

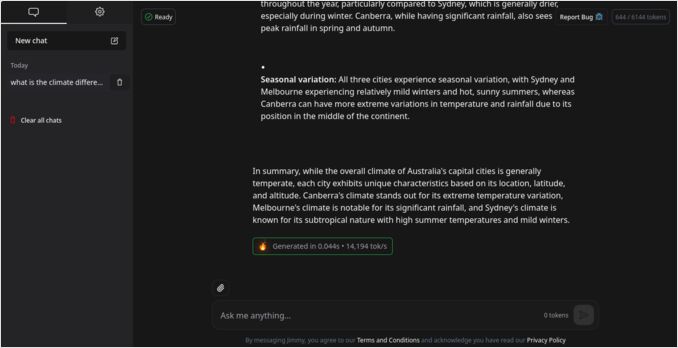

Pour les développeurs qui souhaitent ressentir ce que cela implique en pratique, Taalas propose une démonstration de chatbot gratuite, Chat Jimmy, et offre un accès API via un formulaire d’application sur leur site. C’est explicitement une preuve de concept — pas un assistant de pointe — mais cela illustre un public réel qui pourrait préférer un modèle modeste à une “vitesse de cognition humaine” plutôt qu’un modèle plus grand qui semble lent ou coûteux.

Architecture d’un ASIC d’inférence Transformer

À quoi ressemble réellement une puce optimisée pour les Transformers sous le capot ?

+--------------------------------------+

| Interface Hôte |

| (PCIe / CXL / NVLink / Ethernet) |

+--------------------------------------+

| Interconnexion sur puce (maillage/anneau) |

+--------------------------------------+

| Tuiles de calcul / Cœurs |

| — Unités de multiplication de matrices denses |

| — ALU à faible précision (int8/int4) |

| — Unités de déquantification / Activation |

+--------------------------------------+

| SRAM sur puce & tampons de cache KV |

| — Poids chauds, caches fusionnés |

+--------------------------------------+

| Pipelines de quantification / déquantification |

+--------------------------------------+

| Planificateur / Contrôleur |

| — Moteur d'exécution de graphe statique |

+--------------------------------------+

| Interface DRAM / HBM hors puce |

+--------------------------------------+

Les caractéristiques architecturales clés incluent :

- Cœurs de calcul — Unités de multiplication de matrices denses optimisées pour les opérations int8, int4 et ternaires

- SRAM sur puce — De grands tampons stockent les poids chauds et les caches KV, minimisant les accès DRAM coûteux

- Interconnexions en streaming — La topologie en maillage permet un passage à l’échelle efficace sur plusieurs puces

- Moteurs de quantification — Quantification/déquantification en temps réel entre les couches

- Pile de compilation — Traduit les graphes PyTorch/ONNX directement en micro-opérations spécifiques à la puce

- Cœurs d’attention câblés en dur — Élimine la surcharge de flux de contrôle pour softmax et autres opérations

La philosophie de conception reflète celle des ASIC de Bitcoin : chaque transistor sert la charge de travail spécifique. Pas de silicium gaspillé sur des fonctionnalités dont l’inférence n’a pas besoin.

Benchmarks GPU contre ASIC pour l’inférence LLM

Des figures publiques représentatives montrent comment le matériel d’inférence spécialisé peut s’éloigner des piles GPU à usage général sur les mêmes familles de modèles (vérifiez toujours la méthodologie et les hypothèses de regroupement pour vos propres charges de travail) :

| Modèle | Matériel | Débit (tokens/s) | Temps jusqu’au premier token | Multiplicateur de performance |

|---|---|---|---|---|

| Llama-2-70B | NVIDIA H100 (8x DGX) | ~80–100 | ~1.7s | Référence (1×) |

| Llama-2-70B | Groq LPU | 241–300 | 0.22s | 3–18× plus rapide |

| Llama-3.3-70B | Groq LPU | ~276 | ~0.2s | 3× constant |

| Gemma-7B | Groq LPU | 814 | <0.1s | 5–15× plus rapide |

| Llama-3.1-8B | Taalas HC1 (fournisseur) | ~16k–17k tokens décodés/s/utilisateur | — | Axe séparé (graphe 8B fixe, pas 70B) |

Sources : Groq.com, ArtificialAnalysis.ai, NVIDIA Developer Blog ; chiffres Taalas HC1 issus de l’article produit de l’entreprise.

Les lignes axées sur Groq montrent des gains importants en débit et en temps jusqu’au premier token par rapport à une référence GPU haut de gamme sur les grands modèles. La ligne Taalas n’est pas un autre multiplicateur par rapport à ces lignes 70B ; elle illustre à quel point le décodage par utilisateur peut être poussé lorsque le modèle et le graphe sont figés dans le silicium, au prix de la flexibilité.

Compromis lors de la spécialisation du silicium d’inférence

La spécialisation achète la performance, mais elle réintroduit un risque produit et d’ingénierie :

-

Flexibilité vs Efficacité. Un ASIC totalement figé traverse les modèles Transformer actuels mais pourrait avoir du mal avec les architectures de demain. Que se passe-t-il lorsque les mécanismes d’attention évoluent ou que de nouvelles familles de modèles émergent ?

-

Quantification et Précision. Une précision plus faible économise une quantité massive d’énergie, mais la gestion de la dégradation de la précision nécessite des schémas de quantification sophistiqués. Tous les modèles ne se quantifient pas gracieusement à 4 bits ou moins.

-

Écosystème Logiciel. Un matériel sans compilateurs, noyaux et frameworks robustes est inutile. NVIDIA domine encore largement grâce à l’écosystème mature de CUDA. Les nouveaux fabricants de puces doivent investir massivement dans le logiciel.

-

Coût et Risque. La fabrication d’une puce coûte des dizaines de millions de dollars et prend 12 à 24 mois. Pour les startups, c’est un pari massif sur des hypothèses architecturales qui pourraient ne pas tenir.

Néanmoins, à l’échelle hyperscale, même un gain d’efficacité de 2× se traduit par des milliards d’économies. Pour les fournisseurs de cloud exécutant des millions de requêtes d’inférence par seconde, le silicium personnalisé est de plus en plus non négociable.

Liste de souhaits pour une puce d’inférence LLM

| Fonctionnalité | Spécification Idéale |

|---|---|

| Processus | Nœud 3–5nm |

| SRAM sur puce | 100 Mo+ étroitement couplés |

| Précision | Prise en charge native int8 / int4 / ternaire |

| Débit | 500+ tokens/sec (modèle 70B) |

| Latence | <100 ms jusqu’au premier token |

| Interconnexion | Maillage à faible latence ou liaisons optiques |

| Compilateur | Chaîne d’outils PyTorch/ONNX → microcode |

| Énergie | <0,3 joules par token |

Perspectives (2026–2030)

Attendez-vous à ce que le paysage du matériel d’inférence se stratifie en trois niveaux grossiers :

-

Puces d’entraînement. Les GPU haut de gamme comme NVIDIA B200 et AMD Instinct MI400 continueront de dominer l’entraînement grâce à leur flexibilité FP16/FP8 et leur bande passante mémoire massive.

-

ASIC d’inférence. Des accélérateurs Transformer câblés en dur et à faible précision géreront le service de production à l’échelle hyperscale, optimisés pour le coût et l’efficacité.

-

NPU de bord. Des puces petites et ultra-efficaces apporteront des LLM quantifiés aux smartphones, véhicules, dispositifs IoT et robots, permettant une intelligence sur l’appareil sans dépendance au cloud.

Au-delà du matériel seul, nous verrons :

- Clusters hybrides — GPU pour un entraînement flexible, ASIC (ou moteurs d’inférence à l’échelle de la wafer) pour un service efficace

- Inférence comme service — Les hyperscalers mélangent des accélérateurs de première partie (AWS Inferentia, Google TPU, etc.) avec des GPU

- Conception conjointe matériel–logiciel — Des modèles façonnés pour la sparsité par blocs, le routage MoE et les couches adaptées à la quantification

- Silicium par modèle ou par famille — Des entreprises comme Taalas parient que certains déploiements échangeront la flexibilité architecturale pour un coût et une latence extrêmes sur un graphe connu

- API d’inférence ouvertes — Pression pour maintenir les interfaces de service portables même lorsque le silicium ne l’est pas

Pensées finales

La “ASIC-isation” de l’inférence IA est déjà en cours. Tout comme le minage de Bitcoin a évolué des CPU vers un silicium spécialisé, le déploiement de l’IA} suit la même voie.

La prochaine révolution de l’IA ne portera pas sur des modèles plus gros — elle portera sur de meilleures puces. Le matériel optimisé pour les motifs spécifiques de l’inférence Transformer déterminera qui peut déployer l’IA économiquement à grande échelle.

Tout comme les mineurs de Bitcoin ont optimisé chaque watt gaspillé, le matériel d’inférence pressera chaque dernier FLOP par joule. Lorsque cela arrivera, la véritable percée ne sera pas dans les algorithmes — elle sera dans le silicium qui les exécute.

L’avenir de l’IA se grave dans le silicium, un transistor à la fois.

Pour plus de benchmarks, de choix de matériel et de réglages de performance, consultez notre hub Performance des LLM : Benchmarks, Goulottes et Optimisation.

Liens Utiles

- Benchmarks Officiels Groq

- Taalas — La voie vers une IA ubiquitaire (HC1, feuille de route, philosophie)

- Chat Jimmy — Démo Taalas Llama 3.1 8B

- Formulaire de demande d’accès API Taalas

- Artificial Analysis - Tableau de classement de performance LLM

- Notice Technique NVIDIA H100

- Etched AI - Annonce du Transformer ASIC

- Wafer-Scale Engine de Cerebras

- Prix des NVIDIA RTX 5080 et RTX 5090 en Australie - Octobre 2025

- Performance des LLM et voies PCIe : Points clés à considérer

- Test de vitesse des grands modèles de langage

- Comparaison de l’adéquation des GPU NVIDIA pour l’IA

- Le Quadro RTX 5880 Ada 48GB est-il bon ?