LLM-ASIC:ar och specialiserade inferenschips (varför de är viktiga)

ASIC och skräddarsydd silicium ökar hastighet och effektivitet för LLM-inferens.

Framtiden för AI handlar inte bara om smartare modeller. Det handlar också om kiselbaserad hårdvara som matchar hur dessa modeller faktiskt serveras. Specialiserad hårdvara för LLM-inferens följer en väg som påminner om Bitcoin-gruvdrifts övergång från GPU till specialbyggda ASIC, men med hårdare begränsningar eftersom modeller och precisionsschemat ständigt utvecklas.

För mer information om genomsättning, latens, VRAM och prestandatestningar över olika runtime-miljöer och hårdvara, se LLM-prestanda: Prestandatest, flaskhalsar & optimering.

Elektrisk fantasi - Flux text till bild LLM.

Elektrisk fantasi - Flux text till bild LLM.

Varför LLM:er gynnas av inferensspecifik hårdvara

Stora språkmodeller har förändrat AI, men varje flytande svar beror på enorma, förutsägbara flöden av matrisberäkningar och minnestrafik. Eftersom kostnaden för inferens ökar – ofta och överstiger träningskostnaden under en modells livstid – blir chips som är optimerade för servering, snarare än för alla möjliga arbetslaster, ekonomiskt lockande.

Analogin med Bitcoin-gruvdrift är ofullständig men läraktig. Båda är repetitiva, välavgränsade uppgifter där att ta bort onödig allmängiltighet från chippet kan ge stora vinster i genomsättning och joule per användbar operation.

Vad Bitcoin-gruvdriftens historia säger om inferens-ASIC

Bitcoin-gruvdriften utvecklades genom fyra generationer:

| Era | Hårdvara | Nyckelfördel | Begränsning |

|---|---|---|---|

| 2015–2020 | GPU (CUDA, ROCm) | Flexibilitet | Kraftkrävande, minnesbegränsad |

| 2021–2023 | TPU, NPU | Grov specialisering | Fortfarande träningsorienterad |

| 2024–2025 | Transformer-ASIC | Inställd för låg-bit inferens | Begränsad allmängiltighet |

AI följer en liknande väg. Varje övergång förbättrade prestanda och energieffektivitet med flera storleksordningar.

Men till skillnad från Bitcoin-ASIC (som bara beräknar SHA-256) behöver inferens-ASIC viss flexibilitet. Modeller utvecklas, arkitekturer förändras och precisionsschemat förbättras. Knepet är att specialisera just tillräckligt – att hårdkoda kärnmönstren samtidigt som man behåller anpassningsbarhet vid kanterna.

Hur LLM-inferens skiljer sig från träning (och vad chips utnyttjar)

Inferens-arbetslaster avslöjar mönster som specialiserad hårdvara kan rikta sig mot:

- Låg precision dominerar — 8-bitars, 4-bitars och till och med ternär eller binär aritmetik fungerar bra för inferens

- Minne är flaskhalsen — Att flytta vikter och KV-cachar konsumerar mycket mer energi än beräkning

- Latens är viktigare än genomsättning — Användare förväntar sig token på under 200 ms

- Massiv parallellitet för förfrågningar — Tusentals samtidiga inferensförfrågningar per chip

- Förutsägbara mönster — Transformer-lager är mycket strukturerade och kan hårdkodas

- Möjligheter för sparsamhet — Modeller använder alltmer beskärning och MoE (Mixture-of-Experts) tekniker

Ett syftesbyggt inferenschip kan hårdkoda dessa antaganden för att uppnå 10–50 gånger bättre prestanda per watt jämfört med allmänna GPU.

Vem som bygger inferenssilicon optimerat för LLM

Marknaden för inferens-ASIC sträcker sig från etablerade aktörer och wafer-skala-designer till startups som satsar på transformer-formad silicium:

| Företag | Chip / Plattform | Specialitet |

|---|---|---|

| Groq | LPU (Language Processing Unit) | Deterministisk genomsättning för LLM:er |

| Etched AI | Sohu ASIC | Hårdkodad Transformer-motor |

| Tenstorrent | Grayskull / Blackhole | Allmän ML med högbandbredds mesh |

| Taalas | HC1 (Llama 3.1 8B produkt) / HC2 roadmap | Modell-specifik “hardcore”-silicon; förenar lagring och beräkning |

| OpenAI × Broadcom | Anpassat inferenschip | Ryktats lansering 2026 |

| Intel | Crescent Island | Enbart inferens Xe3P GPU med 160 GB HBM |

| Cerebras | Wafer-Scale Engine (WSE-3) | Enorm bandbredd på chipet minnesbandbredd |

Mycket av detta är redan i produktion i datacenter, inte bara i presentationer. Mindre team som d-Matrix, Rain AI, Mythic och Tenet arbetar också med arkitekturer anpassade för låg-bit inferens och strukturerad sparsamhet.

Taalas HC1, Chat Jimmy och ultra-snabb servering av små modeller

Taalas är ett nyligen exempel på skolan “specialisera nästan allt”. Företaget hävdar att gränsen mellan minne och beräkning (off-chip DRAM kontra on-chip SRAM) dominerar kostnad, strömförbrukning och ingenjörsmässig komplexitet för inferens, och att silicon per modell – vad de kallar Hardcore Models – kan krossa den gränsen när en implementering är villig att fixera vikterna och grafen.

Deras första leveransprodukt, HC1, hårdkodar en variant av Llama 3.1 8B. Det valet är pragmatiskt: modellen är tillräckligt liten för att snabbt sättas igång, öppen dokumenterad och fortfarande användbar för många automatiserings-, klassificerings- och utkastuppgifter där råa resonansdjup väger mindre än latens och kostnad. Taalas rapporterar i storleksordningen 16k–17k decoderade token per sekund per användare för denna konfiguration (leverantörsmetodik och jämförelser finns i deras skrift), tillsammans med påståenden om stora vinster i kapital och ström jämfört med konventionella GPU-stackar för samma modellklass. Delar av första generationen använder aggressiv blandad låg-bitars lagring; företaget beskriver en övergång mot standardiserade 4-bitars flyttal på HC2 för att återfå utrymme på kvalitet.

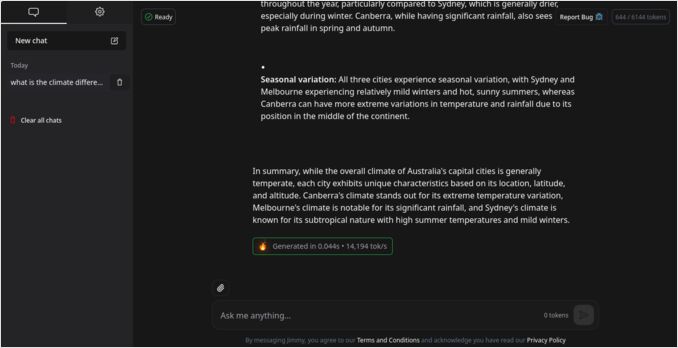

För utvecklare som vill känna vad denna genomsättningsklass innebär i praktiken, kör Taalas en gratis chattbot-demo, Chat Jimmy, och erbjuder API-åtkomst genom ett ansökningsformulär på deras webbplats. Det är explicit en konceptbevis – inte en gränssnittsassistent – men det illustrerar en verklig publik som kanske föredrar en måttlig modell med “människlig kognitiv hastighet” framför en större modell som känns seg eller dyr.

Arkitektur för en transformer-inferens ASIC

Hur ser ett transformer-optimerat chip faktiskt ut under huven?

+--------------------------------------+

| Värdgränssnitt |

| (PCIe / CXL / NVLink / Ethernet) |

+--------------------------------------+

| On-chip Interconnect (mesh/ring) |

+--------------------------------------+

| Beräkningskärnor / Cores |

| — Täta matris-multiplikationsenheter |

| — Lågprecision (int8/int4) ALU |

| — Dekvantiserings-/Aktiveringsenheter |

+--------------------------------------+

| On-chip SRAM & KV-cache-buffrar |

| — Heta vikter, sammanslagna cachar |

+--------------------------------------+

| Kvantiserings-/Dekvantiseringspipelines |

+--------------------------------------+

| Schemaläggare / Kontroller |

| — Statisk grafkörningsmotor |

+--------------------------------------+

| Off-chip DRAM / HBM-gränssnitt |

+--------------------------------------+

Viktiga arkitektoniska funktioner inkluderar:

- Beräkningskärnor — Täta matris-multiplikationsenheter optimerade för int8, int4 och ternära operationer

- On-chip SRAM — Stora buffrar håller heta vikter och KV-cachar, vilket minimerar dyra DRAM-åtkomster

- Strömmande interconnects — Mesh-topologi möjliggör effektiv skalning över flera chips

- Kvantiseringsmotorer — Kvantisering/dekvantisering i realtid mellan lager

- Compilerstack — Översätter PyTorch/ONNX-grafar direkt till chipspecifika mikrooperationer

- Hårdkodade attention-kärnor — Eliminerar kontrollflödesöverskott för softmax och andra operationer

Designfilosofin speglar Bitcoin-ASIC: varje transistor tjänar den specifika arbetslasten. Inget slösilicon på funktioner som inferens inte behöver.

GPU kontra ASIC-benchmarkar för LLM-inferens

Repräsentativa publika siffror visar hur specialiserad inferenshårdvara kan dra ifrån allmänna GPU-stackar på samma modellfamiljer ( verifiera alltid metodik och batchningsantaganden för dina egna arbetslaster):

| Modell | Hårdvara | Genomsättning (token/s) | Tid till första token | Prestanda-multiplikator |

|---|---|---|---|---|

| Llama-2-70B | NVIDIA H100 (8x DGX) | ~80–100 | ~1.7s | Baslinje (1×) |

| Llama-2-70B | Groq LPU | 241–300 | 0.22s | 3–18× snabbare |

| Llama-3.3-70B | Groq LPU | ~276 | ~0.2s | Konsistent 3× |

| Gemma-7B | Groq LPU | 814 | <0.1s | 5–15× snabbare |

| Llama-3.1-8B | Taalas HC1 (leverantör) | ~16k–17k decode t/s/användare | — | Separat axel (fast 8B-graf, inte 70B) |

Källor: Groq.com, ArtificialAnalysis.ai, NVIDIA Developer Blog; Taalas HC1-siffror från företagets produktinlägg.

Raderna fokuserade på Groq visar stora vinster i genomsättning och tid-till-första-token jämfört med en högpresterande GPU-baslinje på stora modeller. Taalas-raden är inte en annan multiplikator mot de 70B-raderna; den illustrerar hur långt per-användare-dekodning kan drivas när modellen och grafen är fastställda i silicium, till priset av flexibilitet.

Avvägningar när man specialiserar inferenssilicon

Specialisering köper prestanda, men den återinför produkt- och ingenjörsmässig risk:

-

Flexibilitet kontra effektivitet. En helt fast ASIC rusar igenom dagens transformer-modeller men kan kämpa med morgondagens arkitekturer. Vad händer när attention-mekanismer utvecklas eller nya modellfamiljer dyker upp?

-

Kvantisering och noggrannhet. Lågare precision sparar enorma mängder energi, men att hantera noggrannhetsförlust kräver sofistikerade kvantiseringsmetoder. Inte alla modeller kvantiserar smidigt till 4-bitars eller lägre.

-

Programvaruekosystem. Hårdvara utan robusta kompilatorer, kärnor och ramverk är värdelös. NVIDIA dominerar fortfarande i stor utsträckning på grund av CUDA:s mogna ekosystem. Nya chip-tillverkare måste investera tungt i programvara.

-

Kostnad och risk. Att “tape out” ett chip kostar tiotals miljoner dollar och tar 12–24 månader. För startups är detta en enorm satsning på arkitektoniska antaganden som kanske inte håller.

Ändå, vid hyperskala, förvandlar till och med 2× effektivitetsvinster till miljarder i besparingar. För molnleverantörer som kör miljontals inferensförfrågningar per sekund, är anpassat silicium alltmer oundvikligt.

En önskelista för en LLM-inferenschip

| Funktion | Idealisk specifikation |

|---|---|

| Process | 3–5 nm processnod |

| On-chip SRAM | 100 MB+ tätt kopplad |

| Precision | int8 / int4 / ternär nativt stöd |

| Genomsättning | 500+ token/sek (70B modell) |

| Latens | <100 ms tid till första token |

| Interconnect | Låglatens mesh eller optiska länkar |

| Compiler | PyTorch/ONNX → mikrokodverktygskedja |

| Energi | <0.3 joule per token |

Framåt (2026–2030)

Förvänta dig att inferenshårdvarulandskapet stratifieras i tre grova nivåer:

-

Träningschips. Högpresterande GPU som NVIDIA B200 och AMD Instinct MI400 kommer fortsätta dominera träning med sin FP16/FP8-flexibilitet och enorm minnesbandbredd.

-

Inferens-ASIC. Hårdkodade, lågprecision transformer-acceleratorer kommer att hantera produktionsservering vid hyperskala, optimerade för kostnad och effektivitet.

-

Edge NPU. Små, ultra-effektiva chips kommer att ta kvantiserade LLM:er till smartphones, fordon, IoT-enheter och robotar, vilket möjliggör intelligens på enheten utan beroende av molnet.

Utöver enbart hårdvara kommer vi att se:

- Hybrida kluster — GPU för flexibel träning, ASIC (eller wafer-skala inferensmotorer) för effektiv servering

- Inferens som en tjänst — Hyperskalare blandar första partens acceleratorer (AWS Inferentia, Google TPU och andra) med GPU

- Hårdvara–programvara samdesign — Modeller formade för blocksparsamhet, MoE-rutning och kvantiseringsvänliga lager

- Silicon per modell eller per familj — Företag som Taalas satsar på att vissa implementeringar kommer att byta arkitektonisk flexibilitet mot extrem kostnad och latens på en känd graf

- Öppna inferens-API — Press för att hålla serveringsgränssnitt portabla även när silicium inte är det

Sluttankar

“ASIC-ifieringen” av AI-inferens har redan inletts. Precis som Bitcoin-gruvdrift utvecklades från CPU till specialiserat silicium, följer AI-implementering samma väg.

Nästa revolution inom AI kommer inte att handla om större modeller – det kommer att handla om bättre chips. Hårdvara optimerad för de specifika mönstren av transformer-inferens kommer att bestämma vem som kan implementera AI ekonomiskt i skala.

Precis som Bitcoin-grävare optimerade bort varje slösad watt, kommer inferenshårdvara att pressa ut varje sista FLOP-per-joule. När det händer, kommer den verkliga genombrottet inte att ligga i algoritmerna – det kommer att ligga i silicium som kör dem.

Framtiden för AI etsas i silicium, en transistor i taget.

För mer benchmarkar, hårdval och prestandajusterings, kolla vår LLM-prestanda: Prestandatest, flaskhalsar & optimering-hub.

Användbara länkar

- Groq officiella benchmarkar

- Taalas — Väg till allomfattande AI (HC1, roadmap, filosofi)

- Chat Jimmy — Taalas Llama 3.1 8B demo

- Taalas API-åtkomst ansökningsformulär

- Artificial Analysis - LLM-prestanda ledarbräda

- NVIDIA H100 teknisk översikt

- Etched AI - Transformer ASIC-annons

- Cerebras Wafer-Scale Engine

- NVidia RTX 5080 och RTX 5090 priser i Australien - oktober 2025

- LLM-prestanda och PCIe-länkar: Viktiga överväganden

- Stora språkmodeller hastighetstest

- Jämförelse av NVidia GPU-lämplighet för AI

- Är Quadro RTX 5880 Ada 48GB bra?