ASICs para LLM y chips especializados de inferencia (por qué son importantes)

Los ASIC y los silicios personalizados impulsan la velocidad y la eficiencia de la inferencia de LLM.

El futuro de la IA no se trata solo de modelos más inteligentes. También se trata de silicio que se adapte a la forma en que esos modelos se sirven realmente. El hardware especializado para inferencia de LLM sigue una trayectoria que recuerda al cambio de la minería de Bitcoin desde las GPUs hacia los ASICs diseñados específicamente, pero con restricciones más estrictas porque los modelos y las recetas de precisión siguen evolucionando.

Para más información sobre el rendimiento, la latencia, la VRAM y los benchmarks en diferentes entornos de ejecución y hardware, consulte Rendimiento de LLM: Benchmarks, Cuellos de Botella y Optimización.

Imaginación Eléctrica - Flux: LLM de texto a imagen.

Imaginación Eléctrica - Flux: LLM de texto a imagen.

¿Por qué los LLM se benefician del hardware específico para inferencia

Los modelos de lenguaje grandes han transformado la IA, pero cada respuesta fluida depende de enormes y predecibles flujos de matemáticas matriciales y tráfico de memoria. A medida que el gasto en inferencia crece —a menudo superando al entrenamiento durante la vida útil de un modelo—, los chips optimizados para el servicio, y no para cada carga de trabajo posible, se vuelven económicamente atractivos.

La analogía con la minería de Bitcoin es imperfecta pero instructiva. Ambas son tareas repetitivas y bien delimitadas donde eliminar la generalidad innecesaria del chip puede comprar grandes ganancias en rendimiento y joules por operación útil.

Lo que la historia de la minería de Bitcoin sugiere sobre los ASICs de inferencia

La minería de Bitcoin evolucionó a través de cuatro generaciones:

| Era | Hardware | Beneficio Clave | Limitación |

|---|---|---|---|

| 2015–2020 | GPUs (CUDA, ROCm) | Flexibilidad | Consumo intensivo de energía, limitado por memoria |

| 2021–2023 | TPUs, NPUs | Especialización de grano grueso | Todavía orientado al entrenamiento |

| 2024–2025 | ASICs de Transformadores | Ajustado para inferencia de bajo bit | Generalidad limitada |

La IA sigue una trayectoria similar. Cada transición mejoró el rendimiento y la eficiencia energética en órdenes de magnitud.

Sin embargo, a diferencia de los ASICs de Bitcoin (que solo calculan SHA-256), los ASICs de inferencia necesitan cierta flexibilidad. Los modelos evolucionan, las arquitecturas cambian y los esquemas de precisión mejoran. El truco es especializar justo lo necesario: cablear los patrones centrales mientras se mantiene la adaptabilidad en los bordes.

Cómo difiere la inferencia de LLM del entrenamiento (y qué explotan los chips)

Las cargas de trabajo de inferencia exponen patrones que el hardware especializado puede atacar:

- La baja precisión domina — La aritmética de 8 bits, 4 bits, e incluso ternaria o binaria funciona bien para la inferencia

- La memoria es el cuello de botella — Mover pesos y cachés KV consume mucha más energía que el cómputo

- La latencia importa más que el rendimiento — Los usuarios esperan tokens en menos de 200 ms

- Paralelismo masivo de solicitudes — Miles de solicitudes de inferencia concurrentes por chip

- Patrones predecibles — Las capas de transformadores son altamente estructuradas y se pueden cablear

- Oportunidades de esparsidad — Los modelos utilizan cada vez más técnicas de poda y MoE (Mezcla de Expertos)

Un chip de inferencia diseñado para el propósito puede cablear estos supuestos para lograr un 10–50× mejor rendimiento por vatio que las GPUs de propósito general.

Quién está construyendo silicio de inferencia optimizado para LLM

El mercado de ASICs de inferencia abarca a empresas consolidadas, diseños a escala de oblea y startups apostando por silicio con forma de transformador:

| Empresa | Chip / Plataforma | Especialidad |

|---|---|---|

| Groq | LPU (Unidad de Proceso de Lenguaje) | Rendimiento determinista para LLMs |

| Etched AI | ASIC Sohu | Motor de Transformadores cableado |

| Tenstorrent | Grayskull / Blackhole | ML general con malla de alto ancho de banda |

| Taalas | HC1 (producto Llama 3.1 8B) / ruta HC2 | Silicio “hardcore” específico del modelo; fusiona almacenamiento y cómputo |

| OpenAI × Broadcom | Chip de Inferencia Personalizado | Lanzamiento rumoreado para 2026 |

| Intel | Crescent Island | GPU Xe3P solo para inferencia con 160 GB HBM |

| Cerebras | Motor a Escala de Oblea (WSE-3) | Ancho de banda de memoria masivo en el chip memory bandwidth |

Gran parte de esto ya está en centros de datos de producción, no en diapositivas. Equipos más pequeños como d-Matrix, Rain AI, Mythic y Tenet también están persiguiendo arquitecturas ajustadas para inferencia de bajo bit y esparsidad estructurada.

Taalas HC1, Chat Jimmy y el servicio ultrarrápido de modelos pequeños

Taalas es un ejemplo reciente de la escuela de “especializar casi todo”. La empresa argumenta que el límite entre memoria y cómputo (DRAM fuera del chip versus SRAM dentro del chip) domina el costo, el consumo de energía y la complejidad de ingeniería para la inferencia, y que el silicio por modelo —lo que ellos llaman Modelos Hardcore— puede colapsar esa frontera cuando una implementación está dispuesta a fijar los pesos y el grafo.

Su primer producto enviado, HC1, cablea una variante de Llama 3.1 8B. Esa elección es pragmática: el modelo es lo suficientemente pequeño para implementarlo rápidamente, está documentado abiertamente y sigue siendo útil para muchas tareas de automatización, clasificación y redacción donde la profundidad del razonamiento bruto importa menos que la latencia y el costo. Taalas reporta un orden de 16k–17k tokens decodificados por segundo por usuario para esta configuración (la metodología del proveedor y las comparaciones aparecen en su documentación), junto con afirmaciones de grandes ganancias en capital y energía frente a pilas de GPU convencionales para la misma clase de modelos. Las partes de primera generación utilizan almacenamiento de bajo bit mixto agresivo; la firma describe un movimiento hacia formatos flotantes estándar de 4 bits en HC2 para recuperar margen en calidad.

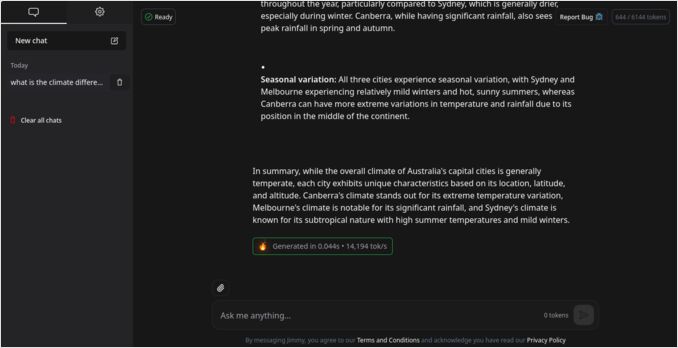

Para los desarrolladores que quieren sentir lo que implica esa clase de rendimiento en la práctica, Taalas ejecuta una demo de chatbot gratuita, Chat Jimmy, y ofrece acceso a la API a través de un formulario de aplicación en su sitio. Es explícitamente una prueba de concepto —no un asistente de vanguardia—, pero ilustra una audiencia real que puede preferir un modelo modesto a “velocidad de cognición humana” sobre un modelo más grande que se sienta lento o caro.

Arquitectura de un ASIC de inferencia de transformadores

¿Cómo se ve realmente un chip optimizado para transformadores bajo el capó?

+--------------------------------------+

| Interfaz del Host |

| (PCIe / CXL / NVLink / Ethernet) |

+--------------------------------------+

| Interconexión en el chip (malla/anillo) |

+--------------------------------------+

| Baldosas/Cores de Cómputo |

| — Unidades de multiplicación matricial densa |

| — ALUs de baja precisión (int8/int4) |

| — Unidades de descuantización / activación |

+--------------------------------------+

| Buffers de caché KV y SRAM en el chip |

| — Pesos calientes, cachés fusionados |

+--------------------------------------+

| Pipelines de Cuantización / Descuantización |

+--------------------------------------+

| Programador / Controlador |

| — Motor de ejecución de grafos estáticos |

+--------------------------------------+

| Interfaz DRAM / HBM fuera del chip |

+--------------------------------------+

Las características arquitectónicas clave incluyen:

- Núcleos de cómputo — Unidades de multiplicación matricial densa optimizadas para operaciones int8, int4 y ternarias

- SRAM en el chip — Buffers grandes almacenan pesos calientes y cachés KV, minimizando los costosos accesos a DRAM

- Interconexiones de transmisión — La topología de malla permite una escalabilidad eficiente entre múltiples chips

- Motores de cuantización — Cuantización/descuantización en tiempo real entre capas

- Pila de compiladores — Traduce grafos PyTorch/ONNX directamente a micro-operaciones específicas del chip

- Kernels de atención cableados — Elimina la sobrecarga del flujo de control para softmax y otras operaciones

La filosofía de diseño refleja a los ASICs de Bitcoin: cada transistor sirve a la carga de trabajo específica. No hay silicio desperdiciado en características que la inferencia no necesita.

Benchmarks de GPU versus ASIC para inferencia de LLM

Figuras públicas representativas muestran cómo el hardware de inferencia especializado puede distanciarse de las pilas de GPU de propósito general en las mismas familias de modelos (siempre verifique la metodología y los supuestos de agrupamiento para sus propias cargas de trabajo):

| Modelo | Hardware | Rendimiento (tokens/s) | Tiempo hasta el primer token | Multiplicador de Rendimiento |

|---|---|---|---|---|

| Llama-2-70B | NVIDIA H100 (8x DGX) | ~80–100 | ~1.7s | Línea base (1×) |

| Llama-2-70B | Groq LPU | 241–300 | 0.22s | 3–18× más rápido |

| Llama-3.3-70B | Groq LPU | ~276 | ~0.2s | 3× consistente |

| Gemma-7B | Groq LPU | 814 | <0.1s | 5–15× más rápido |

| Llama-3.1-8B | Taalas HC1 (proveedor) | ~16k–17k decodificados t/s/usuario | — | Eje separado (grafo fijo de 8B, no de 70B) |

Fuentes: Groq.com, ArtificialAnalysis.ai, Blog de Desarrolladores de NVIDIA; cifras de Taalas HC1 de la publicación del producto de la compañía.

Las filas enfocadas en Groq muestran ganancias grandes en rendimiento y tiempo hasta el primer token frente a una línea base de GPU de alto rendimiento en modelos grandes. La fila de Taalas no es otro multiplicador contra esas líneas de 70B; ilustra hasta qué punto se puede empujar la decodificación por usuario cuando el modelo y el grafo están fijados en silicio, a costa de flexibilidad.

Compromisos al especializar el silicio de inferencia

La especialización compra rendimiento, pero reintroduce el riesgo de producto e ingeniería:

-

Flexibilidad vs. Eficiencia. Un ASIC totalmente fijo atraviesa los modelos de transformadores de hoy, pero podría luchar con las arquitecturas de mañana. ¿Qué sucede cuando los mecanismos de atención evolucionan o emergen nuevas familias de modelos?

-

Cuantización y Precisión. La menor precisión ahorra enormes cantidades de energía, pero gestionar la degradación de precisión requiere esquemas de cuantización sofisticados. No todos los modelos se cuantizan con gracia a 4 bits o menos.

-

Ecosistema de Software. El hardware sin compiladores robustos, kernels y frameworks es inútil. NVIDIA sigue dominando en gran parte debido al ecosistema maduro de CUDA. Los nuevos fabricantes de chips deben invertir fuertemente en software.

-

Costo y Riesgo. Grabar un chip cuesta decenas de millones de dólares y toma de 12 a 24 meses. Para las startups, esto es una apuesta masiva sobre supuestos arquitectónicos que podrían no mantenerse.

Aún así, a escala hipere, incluso las ganancias de eficiencia de 2× se traducen en miles de millones en ahorros. Para los proveedores de nube que ejecutan millones de solicitudes de inferencia por segundo, el silicio personalizado es cada vez más innegociable.

Una lista de deseos de especificaciones para un chip de inferencia de LLM

| Característica | Especificación Ideal |

|---|---|

| Proceso | Nodo de 3–5 nm |

| SRAM en el chip | 100 MB+ fuertemente acoplado |

| Precisión | Soporte nativo int8 / int4 / ternario |

| Rendimiento | 500+ tokens/seg (modelo de 70B) |

| Latencia | <100 ms hasta el primer token |

| Interconexión | Malla de baja latencia o enlaces ópticos |

| Compilador | Cadena de herramientas PyTorch/ONNX → microcódigo |

| Energía | <0.3 julios por token |

Mirando hacia el futuro (2026–2030)

Esperamos que el panorama del hardware de inferencia se estratifique en tres niveles gruesos:

-

Chips de Entrenamiento. Las GPUs de alto rendimiento como NVIDIA B200 y AMD Instinct MI400 continuarán dominando el entrenamiento con su flexibilidad FP16/FP8 y su enorme ancho de banda de memoria.

-

ASICs de Inferencia. Aceleradores de transformadores cableados y de baja precisión manejarán el servicio de producción a escala hipere, optimizados para costo y eficiencia.

-

NPUs de Borde. Chips pequeños y ultraeficientes llevarán LLMs cuantizados a teléfonos inteligentes, vehículos, dispositivos IoT y robots, habilitando inteligencia en el dispositivo sin dependencia de la nube.

Más allá del hardware solo, veremos:

- Clusters híbridos — GPUs para entrenamiento flexible, ASICs (o motores de inferencia a escala de oblea) para servicio eficiente

- Inferencia como Servicio — Los hipereescaladores mezclando aceleradores de primera parte (AWS Inferentia, Google TPU y otros) con GPUs

- Co-diseño hardware–software — Modelos moldeados para esparsidad por bloques, enrutamiento MoE y capas amigables para la cuantización

- Silicio por modelo o por familia — Empresas como Taalas apostando a que algunas implementaciones intercambiarán flexibilidad arquitectónica por costo extremo y latencia en un grafo conocido

- APIs de inferencia abiertas — Presión para mantener las interfaces de servicio portables incluso cuando el silicio no lo sea

Pensamientos finales

La “ASIC-ización” de la inferencia de IA ya está en marcha. Al igual que la minería de Bitcoin evolucionó desde CPUs hasta silicio especializado, el despliegue de IA sigue el mismo camino.

La próxima revolución en IA no se tratará de modelos más grandes, sino de chips mejores. El hardware optimizado para los patrones específicos de la inferencia de transformadores determinará quién puede desplegar IA económicamente a escala.

Al igual que los mineros de Bitcoin optimizaron cada vatio desperdiciado, el hardware de inferencia exprimirá cada último FLOP por julio. Cuando eso suceda, el verdadero avance no estará en los algoritmos, sino en el silicio que los ejecuta.

El futuro de la IA se está grabando en silicio, un transistor a la vez.

Para más benchmarks, opciones de hardware y ajuste de rendimiento, visite nuestro centro de Rendimiento de LLM: Benchmarks, Cuellos de Botella y Optimización.

Enlaces Útiles

- Benchmarks Oficiales de Groq

- Taalas — El camino hacia la IA ubicua (HC1, hoja de ruta, filosofía)

- Chat Jimmy — Demo Llama 3.1 8B de Taalas

- Formulario de solicitud de acceso a la API de Taalas

- Análisis Artificial - Tabla de Clasificación de Rendimiento de LLM

- Breve Técnico de NVIDIA H100

- Etched AI - Anuncio de ASIC de Transformador

- Motor a Escala de Oblea de Cerebras

- Precios de NVidia RTX 5080 y RTX 5090 en Australia - Octubre 2025

- Rendimiento de LLM y Carriles PCIe: Consideraciones Clave

- Prueba de Velocidad de Modelos de Lenguaje Grandes

- Comparación de la idoneidad de GPU NVidia para IA

- ¿Es el Quadro RTX 5880 Ada 48GB Bueno?