LLM 用 ASIC と専門化された推論チップ(なぜ重要なのか)

ASIC とカスタムシリコンが、大規模言語モデル(LLM)の推論速度と効率を推進します。

AI の未来は、より賢い モデル だけに関するものではありません。それは、実際にそれらのモデルがどのように提供されるかに合わせて設計されたシリコン(半導体)についても同様です。LLM の推論 に特化したハードウェアは、ビットコインマイニングが GPU から専用 ASIC へと移行したのと同じような道を行っていますが、モデルや精度のレシピが絶えず進化しているため、より厳しい制約の中で進んでいます。

スループット、レイテンシ、VRAM、ランタイムやハードウェア全体でのベンチマークについては、LLM パフォーマンス:ベンチマーク、ボトルネック、最適化 をご覧ください。

Electrical Imagination - Flux テキストから画像生成 LLM。

Electrical Imagination - Flux テキストから画像生成 LLM。

なぜ LLM は推論専用ハードウェアから恩恵を受けるのか

大規模言語モデル は AI を変革しましたが、すべての流暢な応答は、膨大で予測可能な行列演算とメモリトラフィックのストリームに依存しています。推論コストが増加し(モデルのライフサイクル全体でトレーニングコストを上回ることも多い)、サービス提供に最適化されたチップ(あらゆるワークロードに対応するのではなく)が経済的に魅力的になっています。

ビットコインマイニングとの類推は完全ではありませんが、示唆に富んでいます。どちらも反復的で境界が明確なタスクであり、ダイから不要な汎用性を排除することで、スループットと有用な操作あたりのジュール数を大幅に向上させることができます。

ビットコインマイニングの歴史が推論 ASIC に示唆すること

ビットコインマイニングは 4 つの世代を経て進化しました。

| 時代 | ハードウェア | 主な利点 | 制限 |

|---|---|---|---|

| 2015–2020 | GPU (CUDA, ROCm) | 柔軟性 | 電力消費大、メモリ制約あり |

| 2021–2023 | TPU, NPU | 粗粒度の専門化 | 依然としてトレーニング指向 |

| 2024–2025 | Transformer ASIC | 低ビット推論に最適化 | 汎用性が限定的 |

AI も同様の道を進んでいます。各移行は、パフォーマンス とエネルギー効率を桁違いに向上させました。

しかし、ビットコイン ASIC(SHA-256 のみ計算)とは異なり、推論 ASIC はある程度の柔軟性が必要です。モデルは進化し、アーキテクチャは変化し、精度スキームも改善されます。重要な点は、必要最小限 に特化することです。コアパターンをハードウェア化しつつ、エッジ部分には適応性を維持します。

LLM 推論とトレーニングの違い(そしてチップが活用する点)

推論 ワークロードは、専用ハードウェアがターゲットにできるパターンを露呈します。

- 低精度が支配的 — 8 ビット、4 ビット、さらには 3 値や 2 値演算が推論に適している

- メモリがボトルネック — 重みと KV キャッシュの移動が計算よりもはるかに多くの電力を消費する

- スループットよりレイテンシが重要 — ユーザーは 200ms 未満でトークンを期待する

- 大規模なリクエスト並列処理 — チップあたり数千の同時推論リクエスト

- 予測可能なパターン — Transformer レイヤーは構造化されており、ハードウェア化可能

- スパース性の機会 — モデルは increasingly 剪定や MoE(Mixture-of-Experts)技術を使用している

目的のために設計された推論チップは、これらの仮定をハードウェア化することで、汎用 GPU よりも 10–50 倍のワットあたりのパフォーマンス を実現できます。

LLM 最適化推論シリコンを構築している企業

推論 ASIC 市場には、既存企業、ウェーファスケールの設計、そして Transformer 形状のシリコンに賭けるスタートアップが含まれます。

| 企業 | チップ / プラットフォーム | 特長 |

|---|---|---|

| Groq | LPU (Language Processing Unit) | LLM 向けの決定的なスループット |

| Etched AI | Sohu ASIC | ハードウェア化された Transformer エンジン |

| Tenstorrent | Grayskull / Blackhole | 高帯域メッシュを持つ汎用 ML |

| Taalas | HC1 (Llama 3.1 8B 製品) / HC2 ロードマップ | モデル固有の「ハードコア」シリコン;ストレージと計算を統合 |

| OpenAI × Broadcom | カスタム推論チップ | 2026 年ローンチ噂 |

| Intel | Crescent Island | 推論専用 Xe3P GPU、160GB HBM 搭載 |

| Cerebras | Wafer-Scale Engine (WSE-3) | 巨大なオンチップ メモリ帯域 |

これら多くの技術は、すでにスライド資料ではなく、本番のデータセンターで稼働しています。d-Matrix、Rain AI、Mythic、Tenet などの小規模チームも、低ビット推論や構造化スパース性に調整されたアーキテクチャを追求しています。

Taalas HC1、チャット・ジミー、および超高速小規模モデルの提供

Taalas は、「ほぼすべてを専門化する」学校の最近の例です。同社は、メモリと計算の境界(チップ外 DRAM とチップ内 SRAM)が推論のコスト、電力、エンジニアリングの複雑さを支配しており、モデル固有のシリコン(彼らが「ハードコアモデル」と呼ぶもの)は、重みとグラフを固定することに同意するデプロイメントにおいて、その境界を排除できると主張しています。

最初の出荷製品である HC1 は、Llama 3.1 8B 変種をハードウェア化しています。この選択は実用的です。モデルは素早く立ち上げるのに十分小さく、オープンにドキュメント化されており、生の推論深度よりも レイテンシとコスト が重要な多くの自動化、分類、ドラフト作成タスクで依然として有用です。Taalas は、この構成でユーザーあたり 16k–17k トークン/秒 のデコード速度を報告しており(ベンダーの手法と比較は技術文書に記載)、従来の GPU スタックとの比較において資本と電力の大きな利点を主張しています。初代部品は積極的な混合低ビットストレージを使用しており、同社は HC2 で標準的な 4 ビット浮動小数点形式に移行し、品質の余裕を取り戻すと述べています。

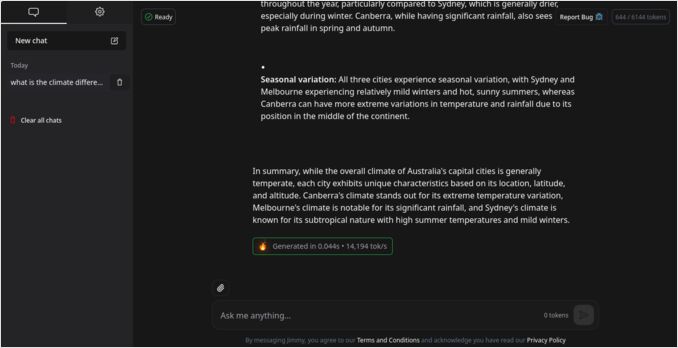

そのスループットクラスが実際に何を意味するかを実感したい開発者のために、Taalas は 無料チャットボットデモ の チャット・ジミー を運営し、サイト上の アプリケーションフォーム を通じて API アクセス を提供しています。これは明確に 概念実証 であり、最先端のアシスタントではありませんが、より大きなモデルが鈍重または高価に感じられる場合、人間の認知速度で動作する控えめなモデルを好む実在するユーザーを示しています。

Transformer 推論 ASIC のアーキテクチャ

Transformer 最適化チップの内部は実際にはどのような見た目でしょうか?

+--------------------------------------+

| ホストインターフェース |

| (PCIe / CXL / NVLink / Ethernet) |

+--------------------------------------+

| オンチップ相互接続 (メッシュ/リング) |

+--------------------------------------+

| 計算タイル / コア |

| — 稠密な行列乗算ユニット |

| — 低精度 (int8/int4) ALU |

| — 量子化解除 / 活性化ユニット |

+--------------------------------------+

| オンチップ SRAM & KV キャッシュバッファ |

| — ホット重み、融合キャッシュ |

+--------------------------------------+

| 量子化 / 量子化解除パイライン |

+--------------------------------------+

| スケジューラ / コントローラー |

| — 静的グラフ実行エンジン |

+--------------------------------------+

| チップ外 DRAM / HBM インターフェース |

+--------------------------------------+

主なアーキテクチャ機能には以下が含まれます。

- 計算コア — int8、int4、3 値演算に最適化された稠密な行列乗算ユニット

- オンチップ SRAM — 大型バッファがホット重みと KV キャッシュを保持し、高価な DRAM アクセスを最小限に抑える

- ストリーミング相互接続 — メッシュトポロジーが複数のチップ間での効率的なスケーリングを可能にする

- 量子化エンジン — レイヤー間でのリアルタイム量子化/量子化解除

- コンパイラスタック — PyTorch/ONNX グラフをチップ固有のマイクロオペレーションに直接変換

- ハードウェア化されたアテンションカーネル — ソフトマックスなどの操作における制御フローオーバーヘッドを排除

設計哲学はビットコイン ASIC を模倣しており、すべてのトランジスタが特定のワークロードに奉仕します。推論に不要な機能に無駄なシリコンはありません。

LLM 推論における GPU と ASIC のベンチマーク

代表的な公開数値は、専用推論ハードウェアが同じモデルファミリーで汎用 GPU スタックからどのように離れるかを示しています(ご自身のワークロードに対して常に手法とバッチングの仮定を確認してください)。

| モデル | ハードウェア | スループット (トークン/秒) | 初回トークンまでの時間 | パフォーマンス倍率 |

|---|---|---|---|---|

| Llama-2-70B | NVIDIA H100 (8x DGX) | ~80–100 | ~1.7s | ベースライン (1×) |

| Llama-2-70B | Groq LPU | 241–300 | 0.22s | 3–18 倍高速 |

| Llama-3.3-70B | Groq LPU | ~276 | ~0.2s | 一貫して 3 倍 |

| Gemma-7B | Groq LPU | 814 | <0.1s | 5–15 倍高速 |

| Llama-3.1-8B | Taalas HC1 (ベンダー) | ~16k–17k デコード t/s/ユーザー | — | 別軸 (固定 8B グラフ、70B ではない) |

出典: Groq.com, ArtificialAnalysis.ai, NVIDIA Developer Blog; Taalas HC1 の数値は会社の製品投稿より。

Groq 中心の行は、大規模モデルにおいてハイエンド GPU ベースラインと比較して、スループットと初回トークンまでの時間で大きな利点を示しています。Taalas の行は、それら 70B の行に対するもう一つの倍率ではありません。モデルとグラフがシリコンに固定された場合、柔軟性を犠牲にしてユーザーあたりのデコードがどこまで押し上げられるかを示しています。

推論シリコンを専門化する際のトレードオフ

専門化はパフォーマンスを購入しますが、製品とエンジニアリングのリスクを再導入します。

-

柔軟性対効率 完全に固定された ASIC は今日の Transformer モデルを駆け抜けますが、明日のアーキテクチャには苦労するかもしれません。アテンション機構が進化したり、新しいモデルファミリーが出現したりしたらどうなるでしょうか?

-

量子化と精度 低精度は莫大な電力を節約しますが、精度の低下を管理するには洗練された量子化スキームが必要です。すべてのモデルが 4 ビット以下に滑らかに量子化するわけではありません。

-

ソフトウェアエコシステム 堅牢なコンパイラ、カーネル、フレームワークがないハードウェアは役に立ちません。NVIDIA は依然として CUDA の成熟したエコシステムのおかげで支配的であり続けています。新しいチップメーカーはソフトウェアに多大な投資をしなければなりません。

-

コストとリスク チップのテープアウトは数千万ドルのコストがかかり、12–24 か月を要します。スタートアップにとって、これはおそらく成立しないアーキテクチャの仮定に対する大きな賭けです。

それでも、ハイ퍼스ケーリングにおいて、2 倍の効率向上ですら数十億ドルの節約につながります。クラウドプロバイダー にとっては、每秒で数百万の推論リクエストを実行しているため、カスタムシリコンはますます不可欠になっています。

LLM 推論チップの願望リスト仕様

| 機能 | 理想的な仕様 |

|---|---|

| プロセス | 3–5nm ノード |

| オンチップ SRAM | 100MB+ 緊密結合 |

| 精度 | int8 / int4 / 3 値ネイティブサポート |

| スループット | 500+ トークン/秒 (70B モデル) |

| レイテンシ | 初回トークンまで <100ms |

| 相互接続 | 低レイテンシメッシュまたは光リンク |

| コンパイラ | PyTorch/ONNX → マイクロコードツールチェーン |

| エネルギー | トークンあたり <0.3 ジュール |

今後の展望 (2026–2030)

推論ハードウェアの景観が 3 つの粗い階層に層化することを期待してください。

-

トレーニングチップ NVIDIA B200 や AMD Instinct MI400 などのハイエンド GPU は、FP16/FP8 の柔軟性と巨大なメモリ帯域により、引き続きトレーニングを支配し続けるでしょう。

-

推論 ASIC ハードウェア化された低精度 Transformer アクセラレータが、ハイパスケールでの本番提供を処理し、コストと効率に最適化されます。

-

エッジ NPU 小型で超効率的なチップが、スマートフォン、車両、IoT デバイス、ロボットに量子化された LLM を持ち込み、クラウド依存なしでオンデバイスインテリジェンスを可能にします。

ハードウェアだけでなく、以下も見ていきます。

- ハイブリッドクラスタ — 柔軟なトレーニング用の GPU、効率的な提供用の ASIC(またはウェーファスケール推論エンジン)

- 推論即サービス — ハイパスケール企業がファーストパーティアクセラレータ(AWS Inferentia、Google TPU など)と GPU を組み合わせている

- ハードウェア–ソフトウェア共同設計 — ブロックスパース性、MoE ルーティング、量子化フレンドリーなレイヤーのために形成されたモデル

- モデル固有またはファミリー固有のシリコン — Taalas などの企業が、既知のグラフにおける極端なコストとレイテンシのためにアーキテクチャの柔軟性をトレードオフするデプロイメントがあることを賭けている

- オープン推論 API — シリコンがなくても提供インターフェースを移植性を保つための圧力

結論

AI 推論の 「ASIC 化」 はすでに進行中です。 ビットコインマイニングが CPU から専用シリコンに進化したように、AI デプロイメントも同じ道を進んでいます。

AI の次の革命はより大きなモデルについてではなく、より良いチップについてです。Transformer 推論の特定のパターンに最適化されたハードウェアが、誰が経済的にスケールして AI をデプロイできるかを決定します。

ビットコインマイナーが浪費されたワットを最適化して排除したように、推論ハードウェアは最後の FLOP/ジュールを絞り出すでしょう。それが起こったとき、真の突破はアルゴリズムではなく、それを実行するシリコンにあるでしょう。

AI の未来は、トランジスタを 1 つずつ、シリコンに刻まれています。

より多くのベンチマーク、ハードウェア選択、パフォーマンスチューニングについては、LLM パフォーマンス:ベンチマーク、ボトルネック、最適化 ハブを確認してください。

有用なリンク

- Groq 公式ベンチマーク

- Taalas — 普遍的な AI への道 (HC1、ロードマップ、哲学)

- チャット・ジミー — Taalas Llama 3.1 8B デモ

- Taalas API アクセスリクエストフォーム

- Artificial Analysis - LLM パフォーマンスリーダーボード

- NVIDIA H100 技術概要

- Etched AI - Transformer ASIC 発表

- Cerebras Wafer-Scale Engine

- NVidia RTX 5080 と RTX 5090 のオーストラリア価格 - 2025 年 10 月

- LLM パフォーマンスと PCIe レーン:重要な考慮事項

- 大規模言語モデル速度テスト

- NVidia GPU の AI 適合性比較

- Quadro RTX 5880 Ada 48GB は良いものか?